咨询电话

400-123-4567

手 机:13988999988

电 话:400-123-4567

传 真:+86-123-4567

邮 箱:admin@baidu.com

地 址:广东省广州市天河区88号

电 话:400-123-4567

传 真:+86-123-4567

邮 箱:admin@baidu.com

地 址:广东省广州市天河区88号

微信扫一扫

Arteris Luan:基于RISC的高性能互连体系结构加速

作者:365bet体育注册日期:2025/07/22 10:17浏览:

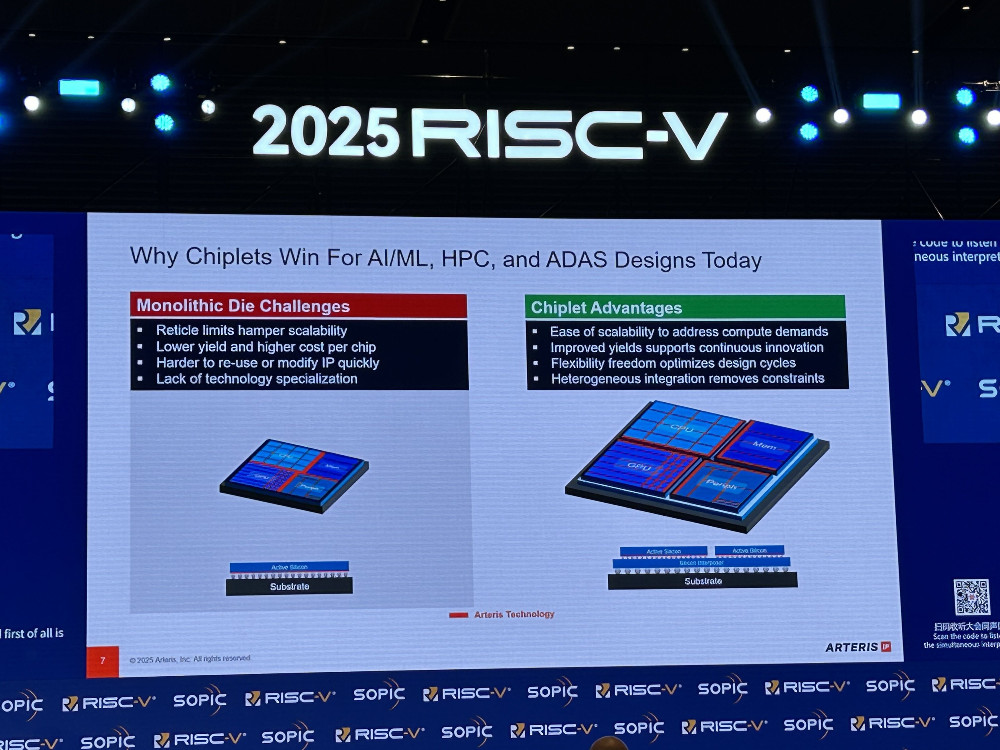

7月18日,第5届RISC-V中国峰会参加了上海的次级课程。作为未来电子行业的最大应用领域之一,人工智能是不可避免的话题。人工智能的快速发展推动了基础建筑的变化,计算强度需求的平均年增长率超过100%。 “开放,灵活和可定制的” RISC-V已成为发展AI计算独立力量的基础的战略支点。人工子部邀请各方的公司讨论RISC-V架构如何使用开放资源,开放和测量的功能来实现AI计算体系结构的变化,以及AI软件和Hardware中RISC-V架构应用程序的最新开发和实施。 Arteris的首席建筑师Luan Jing详细介绍了公司基于AI/ML的基于AI/ML的AI/ML的开发。卢恩·吉(Luan Jing)相信建筑,所以Lintes可以根据RISC-V加速AI和ADAS应用程序,但它增加了常规SOC的复杂性和规模,并带来了下一个挑战级别。对于Internet,Luanjing被列出了一些挑战,例如:我们确实需要扩展总线以进行通信,计算和内存。您会看到建筑物的电线,我们看到越来越多的异源和同构关联,您需要支持常规拓扑和不规则拓扑。根据典型的SOC平面图,您会发现在常规SOC中,我们将在2030年至少拥有5种创新技术,包括登记册,占硅的15%至30%。为了解决这些主要问题并有助于结合复杂的IP,可以在执行区域优化时使用Arteris来优化和执行性能。 SOC面临着发送大量数据的需要,设计师也需要这样做。 i -ximize吞吐量,因为我们需要通过提供记忆计算来减少数据传输的能量Ulations。当然,与此同时,它还必须处理所有RISC-V流程的同构问题,或者可以混合使用武器和其他硬件加速器。最后但并非最不重要的一点是,我们看到该行业开始朝着多芯片和芯片迈进,以及RISC-V部署,从连贯性和ACE作为总线协议开始。这是集成 - 包括异质的,主要与硬件加速器集成在一起的纽斯非常独特,因此我们可以将加速器的数据从加速器带到相干域。要将不同的要求集成到计算元素中,使用芯片可以增加输出,从而大大降低了整体成本。 Luan Jing认为,最重要的是,它允许用户轻松,灵活地在周期的开发中灵活,并方便地从不同的供应商中选择不同的IP,并专注于自己的领域以更改其产品。当然,异质性意味着其他挑战。另一个PECT是整合来自不同技术节点的不同模型,这大大缩短了您的时间窗口的列表,并降低了整体发展成本。另一个流行的消息是,在今年下半年,RTERIS将发布我们的多协同解决方案,随着它的进展,Arteris希望适应行业标准并实现开放的,相互关联的机会。说到ADAS和自动化领域,Luan Jing强调,ADA和自动化市场非常关注现实主义。此外,安全也是一个非常关键的因素。 Arteris有许多工具和机制可供选择,这确实可以帮助客户支持并获得从ASLA到SLD的认证。 Luan Jing认为,在集成和自动化的平台上,IPS真正意识到了一个从IP库到物理设计和SOC的和谐的过程,因为真正的权威不是一个EDA公司或系统IP提供商,但是小型的生态系统需要迭代并结合在一起,并结合在一起来自各方的NE资源,为用户需求创建最合适的解决方案。

7月18日,第5届RISC-V中国峰会参加了上海的次级课程。作为未来电子行业的最大应用领域之一,人工智能是不可避免的话题。人工智能的快速发展推动了基础建筑的变化,计算强度需求的平均年增长率超过100%。 “开放,灵活和可定制的” RISC-V已成为发展AI计算独立力量的基础的战略支点。人工子部邀请各方的公司讨论RISC-V架构如何使用开放资源,开放和测量的功能来实现AI计算体系结构的变化,以及AI软件和Hardware中RISC-V架构应用程序的最新开发和实施。 Arteris的首席建筑师Luan Jing详细介绍了公司基于AI/ML的基于AI/ML的AI/ML的开发。卢恩·吉(Luan Jing)相信建筑,所以Lintes可以根据RISC-V加速AI和ADAS应用程序,但它增加了常规SOC的复杂性和规模,并带来了下一个挑战级别。对于Internet,Luanjing被列出了一些挑战,例如:我们确实需要扩展总线以进行通信,计算和内存。您会看到建筑物的电线,我们看到越来越多的异源和同构关联,您需要支持常规拓扑和不规则拓扑。根据典型的SOC平面图,您会发现在常规SOC中,我们将在2030年至少拥有5种创新技术,包括登记册,占硅的15%至30%。为了解决这些主要问题并有助于结合复杂的IP,可以在执行区域优化时使用Arteris来优化和执行性能。 SOC面临着发送大量数据的需要,设计师也需要这样做。 i -ximize吞吐量,因为我们需要通过提供记忆计算来减少数据传输的能量Ulations。当然,与此同时,它还必须处理所有RISC-V流程的同构问题,或者可以混合使用武器和其他硬件加速器。最后但并非最不重要的一点是,我们看到该行业开始朝着多芯片和芯片迈进,以及RISC-V部署,从连贯性和ACE作为总线协议开始。这是集成 - 包括异质的,主要与硬件加速器集成在一起的纽斯非常独特,因此我们可以将加速器的数据从加速器带到相干域。要将不同的要求集成到计算元素中,使用芯片可以增加输出,从而大大降低了整体成本。 Luan Jing认为,最重要的是,它允许用户轻松,灵活地在周期的开发中灵活,并方便地从不同的供应商中选择不同的IP,并专注于自己的领域以更改其产品。当然,异质性意味着其他挑战。另一个PECT是整合来自不同技术节点的不同模型,这大大缩短了您的时间窗口的列表,并降低了整体发展成本。另一个流行的消息是,在今年下半年,RTERIS将发布我们的多协同解决方案,随着它的进展,Arteris希望适应行业标准并实现开放的,相互关联的机会。说到ADAS和自动化领域,Luan Jing强调,ADA和自动化市场非常关注现实主义。此外,安全也是一个非常关键的因素。 Arteris有许多工具和机制可供选择,这确实可以帮助客户支持并获得从ASLA到SLD的认证。 Luan Jing认为,在集成和自动化的平台上,IPS真正意识到了一个从IP库到物理设计和SOC的和谐的过程,因为真正的权威不是一个EDA公司或系统IP提供商,但是小型的生态系统需要迭代并结合在一起,并结合在一起来自各方的NE资源,为用户需求创建最合适的解决方案。相关文章

- 2025/09/04Liu Qiangdong向Su Chao观众出现

- 2025/09/03Chengdu Rongcheng团队B 2

- 2025/09/02Jilin注册列表更新了:江温兹和库伊·吉林

- 2025/09/01在北京购买Zhao Rui多少钱?新疆媒体透露